Trendande ämnen

#

Bonk Eco continues to show strength amid $USELESS rally

#

Pump.fun to raise $1B token sale, traders speculating on airdrop

#

Boop.Fun leading the way with a new launchpad on Solana.

Jag gick lite vilse i alla akronymer och jargong här, så jag lät Claude förklara det utan att använda några akronymer och nu är allt helt logiskt (tldr; bandbredd ⟹ enkelhet):

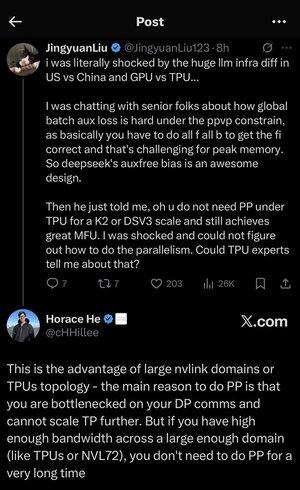

Det här är en fascinerande teknisk diskussion om att träna stora språkmodeller i stor skala.

Kärnan i samtalet

Jingyuan Liu uttrycker förvåning över att ha upptäckt att man inte behöver vissa komplexa optimeringstekniker när man använder TPU:er (Tensor Processing Units - Googles specialiserade AI-chips) kontra GPU:er (Graphics Processing Units - vanligtvis NVIDIA:s chips).

Förklaring av viktiga tekniska begrepp:

Typer av hårdvara:

•GPU (Graphics Processing Unit): Ursprungligen utformad för grafik, men används nu i stor utsträckning för AI. NVIDIA dominerar denna marknad.

•TPU (Tensor Processing Unit): Googles specialdesignade chip speciellt för maskininlärning.

Strategier för parallellitet:

När du tränar massiva AI-modeller måste du dela upp arbetet på många chips. Det finns flera sätt att göra detta:

1Data Parallelism (DP): Varje chip bearbetar olika batcher av data med samma modellkopia

2Tensor Parallelism (TP): Modellens matematiska operationer är uppdelade över kretsar

3Pipeline Parallelism (PP): Olika lager av modellen placeras på olika chips, vilket skapar en pipeline

Den tekniska utmaningen som diskuteras:

Problemet med hjälpförlust: När du tränar mycket stora modeller lägger du ofta till "hjälpförluster" (ytterligare träningsmål) i mellanliggande lager för att hjälpa gradienter att flöda bättre genom nätverket. Under PPVP-begränsningar (Pipeline Parallelism with Variable Partitioning) blir detta komplext eftersom:

•Du måste göra "alla f all b" (alla framåtpassningar, sedan alla bakåtpassningar)

•Detta är en utmaning vid hög minnesanvändning eftersom du måste lagra mellanliggande resultat

DeepSeeks innovation: De utvecklade en "auxfree bias"-design som tydligen undviker att behöva dessa hjälpförluster samtidigt som de tränar effektivt.

Det överraskande avslöjandet:

Den seniora experten berättade för Jingyuan att med TPU:er i K2- eller DSV3-skala (dessa är klusterkonfigurationer med hundratals eller tusentals chips) kan du uppnå utmärkt MFU (Model FLOPs Utilization - i princip hur effektivt du använder hårdvaran) UTAN att använda Pipeline Parallelism.

Varför är detta förvånande?

•Pipelineparallellitet anses vanligtvis vara viktigt för storskalig träning

•Det är en komplex teknik som kräver noggrann optimering

•Att kunna undvika det förenklar allt avsevärt

Horace He's Förklaring:

Han förklarar VARFÖR detta är möjligt med TPU:er:

Fördelen med bandbredd: TPU:er och avancerade NVIDIA-kluster (som NVL72 - NVIDIA:s senaste 72-GPU-konfiguration med NVLink-anslutningar) har så hög bandbredd mellan kretsarna att de kan hantera kommunikationskraven utan Pipeline Parallelism.

Den viktigaste insikten:

•Pipelineparallellitet behövs främst när du är "flaskhals på DP-kommunikation" (begränsas av hur snabbt du kan kommunicera under parallell träning av data)

•Om du har tillräckligt med bandbredd över en tillräckligt stor domän (sammankopplad kluster) kan du bara använda enklare strategier för parallellitet

•Detta fungerar "under mycket lång tid" - vilket innebär att du kan träna även mycket stora modeller utan att nå gränserna

Intuitionen:

Tänk på det som ett motorvägssystem:

•Traditionella GPU-kluster är som att ha smala vägar mellan städer, så du behöver komplex routning (Pipeline Parallelism) för att undvika trafikstockningar

• TPU-kluster eller NVLink-anslutna GPU:er är som att ha enorma motorvägar - du kan bara skicka allt direkt utan avancerad routing

Det här är en stor sak eftersom pipelineparallellitet är komplicerat att implementera, felsöka och optimera. Att kunna undvika det samtidigt som man uppnår hög effektivitet gör hela träningsprocessen mycket enklare och mer tillförlitlig.

Diskussionen belyser hur framsteg inom hårdvarusammankopplingsteknik ("vägarna" mellan chip) i grunden kan förändra de mjukvarustrategier som behövs för effektiv AI-träning.

3,51K

Topp

Rankning

Favoriter