Tópicos em alta

#

Bonk Eco continues to show strength amid $USELESS rally

#

Pump.fun to raise $1B token sale, traders speculating on airdrop

#

Boop.Fun leading the way with a new launchpad on Solana.

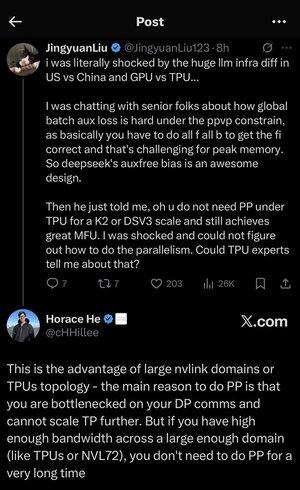

Eu me perdi um pouco em todas as siglas e jargões aqui, então pedi ao Claude que explicasse sem usar nenhuma sigla e agora tudo faz todo o sentido (tldr; largura de banda ⟹ simplicidade):

Esta é uma discussão técnica fascinante sobre o treinamento de grandes modelos de linguagem em escala.

A conversa central

Jingyuan Liu está expressando surpresa ao descobrir que você não precisa de certas técnicas complexas de otimização ao usar TPUs (Tensor Processing Units - chips de IA especializados do Google) versus GPUs (Graphics Processing Units - normalmente chips da NVIDIA).

Principais conceitos técnicos explicados:

Tipos de hardware:

•GPU (Unidade de Processamento Gráfico): Originalmente projetada para gráficos, agora muito usada para IA. A NVIDIA domina esse mercado.

• TPU (Tensor Processing Unit): os chips personalizados do Google especificamente para aprendizado de máquina.

Estratégias de paralelismo:

Ao treinar modelos massivos de IA, você precisa dividir o trabalho em vários chips. Existem várias maneiras de fazer isso:

1Paralelismo de dados (DP): Cada chip processa diferentes lotes de dados com a mesma cópia do modelo

2Paralelismo tensorial (TP): as operações matemáticas do modelo são divididas em chips

3Paralelismo de pipeline (PP): Diferentes camadas do modelo são colocadas em diferentes chips, criando um pipeline

O desafio técnico em discussão:

O problema de perda auxiliar: ao treinar modelos muito grandes, você geralmente adiciona "perdas auxiliares" (objetivos de treinamento adicionais) em camadas intermediárias para ajudar os gradientes a fluir melhor pela rede. Sob restrições de PPVP (paralelismo de pipeline com particionamento variável), isso se torna complexo porque:

• Você precisa fazer "all f all b" (todas as passagens para frente, depois todas as passagens para trás)

•Isso é um desafio para o pico de uso de memória porque você precisa armazenar resultados intermediários

Inovação da DeepSeek: Eles desenvolveram um design de "viés auxfree" que aparentemente evita a necessidade dessas perdas auxiliares enquanto ainda treina de forma eficaz.

A revelação surpreendente:

O especialista sênior disse a Jingyuan que, com TPUs na escala K2 ou DSV3 (são configurações de cluster com centenas ou milhares de chips), você pode obter uma excelente MFU (Utilização de FLOPs de Modelo - basicamente com que eficiência você está usando o hardware) SEM usar o paralelismo de pipeline.

Por que isso é surpreendente?

•O paralelismo de pipeline é normalmente considerado essencial para treinamento em larga escala

•É uma técnica complexa que requer uma otimização cuidadosa

• Ser capaz de evitá-lo simplifica tudo significativamente

Horace Ele é a explicação:

Ele explica POR QUE isso é possível com TPUs:

A vantagem da largura de banda: TPUs e clusters NVIDIA de ponta (como NVL72 - a mais recente configuração de 72 GPUs da NVIDIA com interconexões NVLink) têm largura de banda tão alta entre os chips que podem lidar com os requisitos de comunicação sem paralelismo de pipeline.

O principal insight:

•O paralelismo de pipeline é necessário principalmente quando você está "com gargalo nas comunicações DP" (limitado pela rapidez com que você pode se comunicar durante o treinamento paralelo de dados)

•Se você tiver largura de banda suficiente em um domínio grande o suficiente (cluster interconectado), poderá usar estratégias de paralelismo mais simples

•Isso funciona "por muito tempo" - o que significa que você pode treinar até mesmo modelos muito grandes sem atingir os limites

A intuição:

Pense nisso como um sistema de rodovias:

•Os clusters de GPU tradicionais são como ter estradas estreitas entre as cidades, então você precisa de roteamento complexo (paralelismo de pipeline) para evitar engarrafamentos

• Clusters TPU ou GPUs conectadas a NVLink são como ter superrodovias enormes - você pode simplesmente enviar tudo diretamente sem roteamento sofisticado

Isso é importante porque o paralelismo de pipeline é complexo de implementar, depurar e otimizar. Ser capaz de evitá-lo enquanto ainda alcança alta eficiência torna todo o processo de treinamento muito mais simples e confiável.

A discussão destaca como os avanços na tecnologia de interconexão de hardware (as "estradas" entre os chips) podem mudar fundamentalmente as estratégias de software necessárias para um treinamento eficiente de IA.

3,62K

Melhores

Classificação

Favoritos